主题:同学们,“半导体存储器导论课”第二课开始点名,分组讨论了, -- 老瑞

p-substrate的话?猜的,要南越老大回答.

n/p都可以。但是这么深的poly-Si,不太容易掺杂啊。

花!

能否将半导体存储器件分类的这部分重新组织一下,

另外配几个示意图。

像是DRAM的1T1C结构的之类的,没有图的话,可能很多人看的迷迷糊糊的。![]()

因为,我发现咱们班同学很多都是对这个课题有兴趣,但本职工作与半导体行业差的挺远的。

这篇短文充实一点内容,配几个图,

做为咱们课程的

【第二课】 半导体存储器的分类(V1.0),主讲老师:南越

咱们这个班里就是互动讨论式的,每个人都可以做老师的,

把自己知道的讲出来,跟大家讨论讨论,

学到的东西应该更多。![]()

期待您的第二课早日开课!![]()

鲜花已经成功送出。

此次送花为【有效送花赞扬,涨乐善、声望】

“南越”兄的文章更接近器件本身,

实际器件就是设计成那样的,

一是一,二是二,很明了。

而且“南越”兄的文笔很洗练,而且容易懂。

俺初步的重点是放在器件原理的介绍上。

对于原理的理解,可能费点劲。

而且,机理也是一个不断完善的过程,

我们现在对有些过程也不能做太绝对的论断。![]()

不过,看了看老兄的文章,

好像都是些“性感”的文章啊,哦,是“感性”的文章![]()

怎么也来俺们这里混着听课啊?

那只好打PP了,

“老班长”那,“班法”伺候,

![]()

慢慢看,等看到了半导体存储器的详细分类以后,

您的疑问就可以慢慢解开了,![]()

您讲的俺没学过,所以俺不懂,

毕业很多年了,专业知识都忘的差不多了,

看您讲课,俺想做个认真学生,过来旁听一下,

好好学习,天天向上!![]()

不好意思,俺写的文字都是些小女人文字。呵呵

瑞老师,您继续讲,俺认真听。

俺们当年跟物理系自动化专业的一起上“普通物理课”,

课本好像差别不大,

“巨磁电阻”是比较新的概念,那时候的课本好像没有,

老兄现在还做自动化吗?

毕业以后就再没碰过,不过电脑知识还是因为学专业时了解一些。我们当时学一些芯片什么的,还有模拟电路数字电路等等,现在看着这些名字还感觉亲切。当时很喜欢做芯片电路设计,两侧全是引线,像百爪蜈蚣,![]()

那这么说来,咱们早就是同学啦,![]()

您也多写您的文字,读起来很亲切的说,

这里的水太深了,我常是默默地看,不敢多言,老师还是老瑞您,我刚好工作与这不远,能写的我会尽量,欢迎拍砖。

(2)凑数的说说闪存(Flash memory)

Flash memory 有NAND 和NOR型,这都是元东芝的叫外冈富士雄的研究员在1987年发明的(这老兄也与东芝打了奖金的官司现在像到东北大当教授了)。由于NOR型写入速度不高,线路不易微细化,现在常说的闪存都是NAND型。下图就是NAND型闪存的一个cell的微结构示意图。

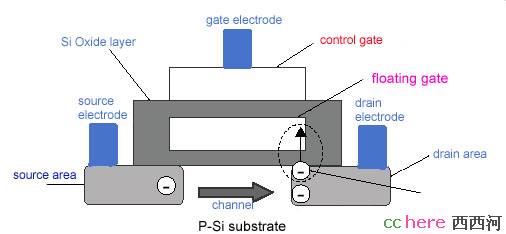

与我前面介绍过的DRAM相比,它没有了电容,只是在MOS的结构上改了,做了个两层的gate,上层的gate是控制gate与word line连接,下层的gate 是形成于Si基板表面氧化物层上,其与上层的gate也隔着一层氧化物层,称为浮游gate, 就是靠它的带电来实现存储,初期状态无电子为1,有电子时为0。

在0的写入时,gate电极和drain电极间加高电压,使得drain部的电子突破氧化物层的能垒,靠隧道效应进入浮游gate, 如此,断电时浮游gate内的电子由周围的氧化物膜来绝缘保持,从而实现了不挥发性。

读数据时,给gate电极上加上电压来导通MOS, 存储了数据0的cell由于drain部的电子进入到了浮游gate而导致流过channel 的电流相对较小。也就是说,gate电极加一定的电压后,流入bit线的电流大的cell存储的是1,反之是0。

看到这,就可看出NAND flash memory的优点哪,它可以多个cell共有控制的导线而简单化,由此数据的读写可以用称为一页的方式来进行,旧型号的NAND一般是一页512 byte, 现在新型的电极配线已为40纳米,一页为2014byte。它的数据读出速度是50ns,但写入就慢了据说为1s;再者浮游gate周围的氧化物膜由于经常使用而劣化,导致写入数据0时过量的电子进入浮游gate,读数据时,该cell的电压发生异常而出错。这就是flash memory的大问题,想必很多人都有过数据读不出的经历。尽管NAND在设计上每一页都配有存储纠错的另外的byte来更新而格式化。